IC(Integrated Circuit, 集積回路)はPCやスマートフォンをはじめとしたあらゆる電子機器に搭載されており、今日のICT・IoT社会をその根底から支えています。

これから先、ICはどのように変化し、どのような未来を形作っていくでしょうか。ここではまず時代を遡って、ICの辿ってきた歴史からその有り様を紐解いてみることにします。

ICの誕生とスケーリング

1950年代の終わる頃、技術者たちはある問題に直面していました。それは、膨大な部品から成る電子機器をどのような方法で作っていくかというものでした。電子機器を構成する部品点数の増大にしたがって、部品間を接続するための配線は急激に増加し複雑化していきます。基板上に複数の異なる電子部品を配置していく当時の開発手法では、こうした部品間の配線や半田付けを手作業でおこなう必要がありました。これによって電子回路の性能やサイズの改善は妨げられ、故障率は悪化し、製造コストは増大していきます。小型なトランジスタの発明によって巨大な真空管が置き換えられ、電子回路の応用先がいよいよ民生機器にまで拡がろうとする中、この ”Tyranny of Numbers” (数の横暴)と呼ばれる課題に対する抜本的な解決策を見つけることが急務となっていました。

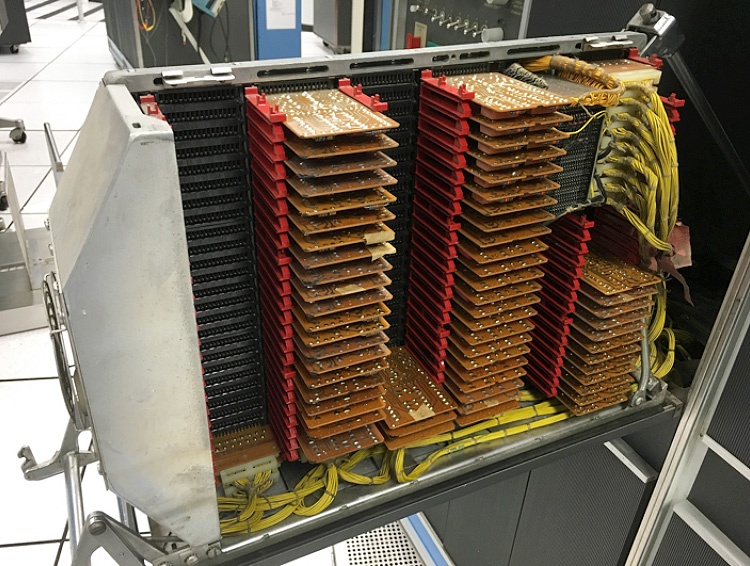

1959年に発表されたIBM 1401の内部

(写真: ArnoldReinhold CC-BY-SA-3.0)

こうした背景のもと生まれたのが、ICです。当時、米国のTexas Instrumentsでは多数の部品をより小さな面積の基板へと実装するための技術開発が進められていました。同社の社員であったジャック・キルビーはその方針に沿いながら、よりラディカルな刷新を提案します。それは、従来のように複数の部品を基板上に配置し配線するのではなく、半導体でできた小さな1枚のチップ上に全ての部品を集積しチップ上で接続してしまうというものでした。これが現在のICへと繋がるアイディアです。

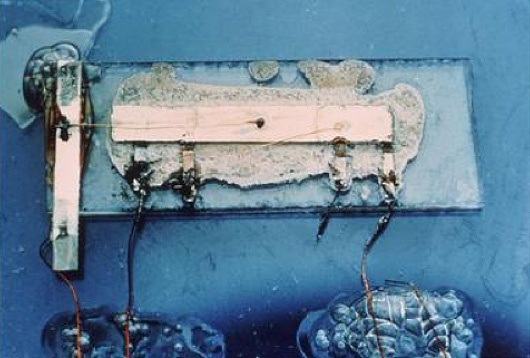

Jack Kilbyによる世界初のIC

1.3cmに満たないサイズに複数の素子が集積されている

(写真: https://en.wikipedia.org/wiki/Integrated_circuit)

共通のチップ上に複数の部品素子を集積し接続する手法が拓かれたことで、膨大な手配線の時代は終わり、小型な電子回路の大量生産が可能になりました。ICは大きな注目を集め、1965年には「ICに搭載される素子数はこれまで1年に2倍の割合で増加しており、少なくとも今後10年間はそのトレンドが続くだろう。すなわち1975年には、ICの素子数は65000に達するであろう」という、今日 “ムーアの法則” として知られる予言が為されることになります。驚くべきことに、この当時のICにはたった64個の素子しか集積されていませんでした。しかしながら、この予言の通りICは指数的な成長を続け、現在では100億個以上のトランジスタが単一チップ上に搭載されるまでになっています。

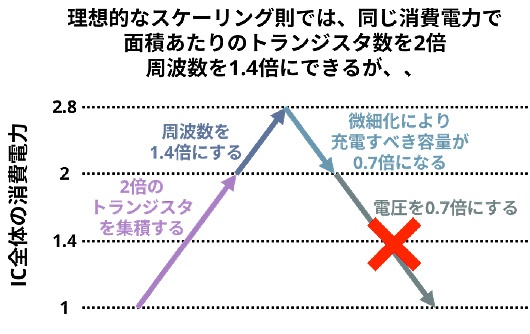

それでは、ICはなぜこのように特異的な成長を継続することができたのでしょうか?その背景には、スケーリング則と呼ばれる理論的な裏付けがあります。トランジスタのサイズを小さくすると、当然ながら同じ面積に集積できるトランジスタの数を増やすことができます。しかしそれだけではなく、負荷となる容量が減ることで動作速度が向上します。更には、より低い電圧によってトランジスタを動作させることができるようになります。たとえば、トランジスタを0.7倍のサイズにすると、トランジスタの数は2倍になり、動作速度は1.4倍になり、0.7倍の電圧で動作させることができる——といったことが、理論的に示されています。こうした技術的な裏付けに基づく微細化・高集積化という、極めて明確な成長指針があったために、ICは飛躍的な進化を続けることができたのです。

多くの工学分野では、性能や電力、製造コストの間にトレードオフが生じます。そうした中でICやそれを基盤とする産業は、「ただスケーリングを突き進めていけば、高性能化と省電力化、低コスト化を一挙に達成できる」というある種享楽的な ”フリーランチ” の状況下に長くありました。

電力との闘い

しかしながら、2000年代に差し掛かった頃からそうした堅調な成長にも翳りが見え始めています。デメリットなくスケーリングを推し進めるためには、トランジスタの微細化と共に加える電圧を低下させ、面積あたりの電力を一定に保つ必要があります。ところが、高性能化の優先や、周辺に配置するICとの整合性保持のため、電圧のスケーリングは長らく停滞していました。更には一つのトランジスタのサイズが90nm(ナノメートル、10億分の1メートル)以下、という極度の微細化に伴ってトランジスタのリーク電流増加が深刻な課題となり始め、これを緩和するために電圧の低減はますます鈍化していきました。つまり、単に微細化と高速化を推し進めてしまうと、同一面積あたりの電力は増加の一途を辿っていくようになりました。

ところで、PCに搭載されるCPUのクロック周波数のトレンドを眺めてみると、2000年代の初め頃からその値にほとんど変化の無いことがわかると思います。実際、最近はそれほどPCの性能が上がっていない、と感じている方も多いのではないでしょうか。上に示した図から明らかなように、電圧を下げることなく電力を一定に保とうとすれば、トランジスタの集積度や周波数の向上は諦めざるを得ません。そこで産業界では周波数向上に見切りを付け、別の手法(たとえば、マルチコア化)での性能改善を図っている、という現状があります。

とはいえマルチコア化による性能改善にも限界があるため、技術的なブレークスルーが無い限り「高性能化(トランジスタ数の向上か、周波数の向上)を推し進めると、どうしても電力が増加してしまう」という状況へと進んで行くことが予想されます。こうした傾向を言い換えたものが即ち「微細化によってトランジスタの集積度向上が達成できても、電力の制約から同時にすべてのトランジスタを稼動できなくなる」という ”ダークシリコン問題” です。

ここに示したようなスケーリング則の根本的破綻や物理限界、更にはnmオーダの極微細加工に伴う設備投資額の急増という経済的課題が重なったことで、近年 “ムーアの法則の終焉” がいたるところで囁かれています。

ICの現在地

伝統的なスケーリング則に基づく性能向上シナリオが限界を迎えつつあるいま、ICを巡る技術開発には新たな潮流が興りはじめています。ここでは、”ヘテロジニアス・コンピューティング” や ”ICのオープン・イノベーション” といったトピックに目を向けてみましょう。

スマートフォンはいまや生活の中心を担うデバイスとなっています。その内部では複数の回路部品が精緻に組み合わさっていますが、更にレイヤを降って主要なICチップの中を覗いてみると、そこには多くの異なるプロセッサコアが存在していることがわかります。このように複数の異なるプロセッサコアで構成されたICをヘテロジニアス・マルチコアSoC(System on a Chip)と呼びます。

ヘテロジニアス・マルチコアには、前に述べた “ダークシリコン問題” への対応策という側面があります。通常のマルチコアプロセッサを採用すると、電力の制約から8つのCPUコアしか稼動できない場合について考えてみましょう。すると、仮に8個より多くのCPUコアをICに搭載したとしても、その部分は同時に動かすことが出来ないため無駄なダークシリコンとなってしまいます。一方、ヘテロジニアス・マルチコアの構成では、CPUだけではなく異なる複数のコアをICに搭載しています。本来であればダークシリコンとして無駄になってしまう部分を、特定のワークロードをターゲットとする専用プロセッサコア(アクセラレータ)で埋めています。こうすることで、通常のワークロードにおける消費電力を抑えつつ、特定のワークロードにおいてはCPUではなく専用アクセラレータコアを利用することで、CPUだけを使う場合よりも効率よく処理をおこなうことができます。

特にバッテリの制約から低消費電力化が求められるスマートフォンやその他のエッジデバイスにおいては、ヘテロジニアス・マルチコアSoCが一般的なシステム構成手法となりつつあります。たとえば、多くのAndroidスマートフォンに搭載されているQualcommのSnapdragonや、AppleのiPhoneに搭載されているA11、Huaweiのスマートフォンに搭載されているHiSiliconのKirinは、どれも極めて似た構成のヘテロジニアス・マルチコアSoCとなっています。

一方で、IC開発におけるオープン・イノベーションとも呼ぶべき流れが進んでいます。ICの内部には膨大な回路が集積されており、その全てを設計・検証することは容易ではありません。そのため多くのIC開発現場において、設計・検証済みの出来合いの回路(IPコア)を高額なライセンス料と引き換えに他社から調達し利用する、ということがおこなわれています。各々の回路の仕様や設計ノウハウは、産業競争力であると共にそうしたIPコアビジネスにおけるライセンス料の源でもあり、従来は回路を開発した企業の中で秘匿されるというのが常識でした。しかし、そうした状況にも変化が起こりつつあります。

近年、低価格のIPコアを組み合わせることによって超短期間でのIC開発をおこなうファブレス半導体企業が隆盛しており、それと並行して安価にIPコア開発を請け負う企業も現れ始めています。また、こうしたIPコア導入コスト削減の裏返しとして、設計データや設計開発ノウハウのオープン化が段々と進んでいます。個人的な体験として、数年前まではIC設計ツールに関する情報をネット上で検索してもほとんど見つけることの出来なかったのが、最近では個人の書いた技術ブログが次々とヒットするようになったことに驚いています。背景にはソフトウェア分野におけるOSS開発の成功もあるかもしれません。

こうした一連の流れの中でも極めて大きな注目を浴びているのは、オープンな命令セットアーキテクチャ(ISA)であるRISC-Vでしょう。これまでにもオープンライセンスな命令セットは存在しましたが、多くは実用性や開発エコシステムに難点があると指摘されていました。RISC-Vは洗練された設計や今後の開発環境拡充の期待により、学術研究の世界から産業界に至るまで広く関心を集めています。これまでの商用プロセッサに用いられてきた複雑な命令セットと比較すると極めて明瞭な構成になっており、特定用途プロセッサ向けに命令を拡張することも容易になっています。つまり、RISC-Vは前述したヘテロジニアス・マルチコア構成と専用プロセッサによるICの性能改善シナリオを見据えたものでもあります。大学の研究室や、ベンチャー企業が開発の中心となり「ハードウェアのアジャイル開発」を謳って次々に試作ICや製品を発表しているのも面白いところです。自社で競争力のある専用プロセッサを開発可能な企業がRISC-V ISAを採用するメリットは大きいと思われるため、今後更に多くの製品へ取り入れられていきそうです。

私が未踏事業でチームのリーダーとして開発をおこなった「DragonASIC」も、こうした流れに対応するプラットフォームです。「DragonASIC」はWebアプリケーションであり、ブラウザ上での簡単なソフトウェア記述と、搭載するセンサやインタフェース回路の選択のみによってICを設計することが可能です。従来のIC設計ツールが要求する専門的な知識や高額な導入コストは必要なく、容易、かつ短期間にカスタムICを開発することができます。

ICの未来

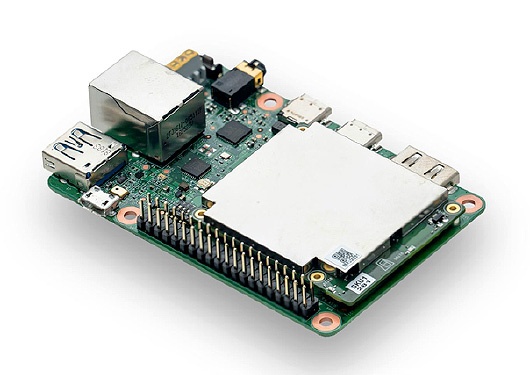

これから、前述したヘテロジニアス化を引き継ぐかたちで、ますます多くのモノに、多様でアプリケーション特化なプロセッサコアが混載されていくでしょう。たとえば、深層学習の推論処理向けアクセラレータは既に多大な関心を集めており、この先も新たなアーキテクチャの開発や、既存のシステムとの統合が進められていくでしょう。現在では多くのスマートフォンに専用コアの一つとして組み込まれる様になったほか、intelのMyriadのような専用チップもUSBデバイスの形で利用可能になっています。今年の秋には強力なソフトウェア開発エコシステムに支えられたGoogleのEdge TPUとその開発用ボードの販売が予定されており、今後益々の流行となっていきそうです。

Google Edge TPU Dev Board

(写真: https://aiyprojects.withgoogle.com/edge-tpu)

この先数年は、こうした個々の専用プロセッサアーキテクチャの革新と、チップの三次元実装のようなパッケージング技術の進展によってICは成長していくことになりそうです。更に先を見れば、新材料や、量子コンピュータ、シリコンフォトニクスの時代もやってくるかもしれません。しかし、こうした種々の新手法のうち何れかが万能の設計指針として未来のICを形作っていくというよりは、得意分野の異なる様々なデバイスやアーキテクチャを組み合わせた複雑なシステムが、未来のICの姿ということになりそうです。つまり、ICがIC以前とも似た複雑怪奇な代物へとある意味で回帰していくことに疑いの余地は無く、高度にヘテロジニアスなシステムを巧妙に構築していく設計開発手法の確立が今後大きな課題になりそうです。これはソフトウェアのレイヤについても言えることで、ヘテロジニアスなハードウェアを統括する優れたシステムソフトウェアの開発は極めて重要な仕事となっていくでしょう。

ここまで述べて来たように、ICは「どのように複雑な回路を統合し、高性能なシステムを構築するか」という課題の解決策として誕生しました。魔術的なスケーリングの時代を通り過ぎて、我々は今一度、このシステム設計に纏わる根源的な難題と、個々の回路の高性能化の要求とに向き合っているといえます。言い換えればこれは全く新しいIC、全く新しいアーキテクチャを生み出す契機がようやく到来したということです。IC開発に携わる企業や大学のエンジニアにとっては、黎明期以来の刺激的で心躍る時代がやってきたのかもしれません。とはいえ、スケーリングによる飛躍的な成長の時代に較べてみると、ICが平凡な一技術になりつつあるのではないか、という寂しさをどこかに感じることも事実です。

さて、果たしてICはこうした漸進的な進展に満足するのでしょうか。微細化が止まったとき、また別の革新的な技術によって指数的な成長は維持されていくのだ、と予想する人もいます。今後の成長を支える新たな革新が、まだどこかで息を潜めてはいないだろうか、そうした考えにも耽りつつ、今は真夏の茹だる暑さの中この原稿を書いています。そういえば、ジャック・キルビーが革命的なICの開発に成功したのも夏の盛り、一人黙々と社内で作業している際のことでした。ともすれば、今にも何処かで次の萌芽が———そんなこともあるかもしれません。

門本 淳一郎

東京大学 大学院 情報理工学系研究科 博士課程

2017年度未踏事業に「GUIによるカスタムマイコン設計プラットフォーム」で採択され、Webブラウザ上でのカスタムIC設計を可能にするプラットフォーム「DragonASIC」を開発する。大学院でCPUアーキテクチャや三次元SiPについて研究をおこないつつ、ベンチャー企業で製品開発に携わっている。趣味は手描きCPU作り。